Xiphera launches two new Intellectual Property (IP) cores for the Random Number Generation product family. These are the balanced and high-speed versions of a Pseudorandom Number Generator (PRNG) which provide the user with random data at the speed of gigabits or even tens of gigabits per second. A PRNG is often used in applications, where lots of random data is needed, for example in the generation of session-specific secret key material in core network routers.

Randomness is a crucial component of all cryptography. If encryption or signature protocols were strictly deterministic, or in other words, not random, they could easily be broken. But how do we introduce randomness into these protocols?

Answer: random number generators. Random number generators come in two flavours: True Random Number Generators (TRNG) which are based on physical random phenomena, and Pseudorandom Number Generators (PRNG) which produce random-looking outputs from a given seed. A combination of the two, that is, when a PRNG is seeded with a TRNG, we have what is known as Cryptographically Secure Random Number Generator, or CSRNG.

Since randomness is a critical topic for cryptography, the requirements for both TRNGs and PRNGs have been standardised, most notably by the American National Institute of Standards and Technology (NIST). Xiphera’s Random Number Generation portfolio fully complies with the SP800-90 standard series, which consists of three parts: 90A for PRNG, 90B for TRNG, and 90C for CSRNG.

Balanced and high-speed PRNG from Xiphera

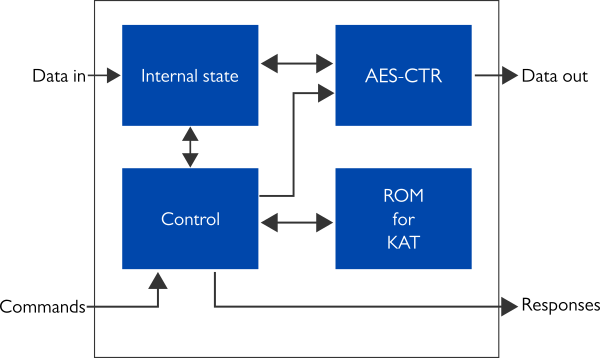

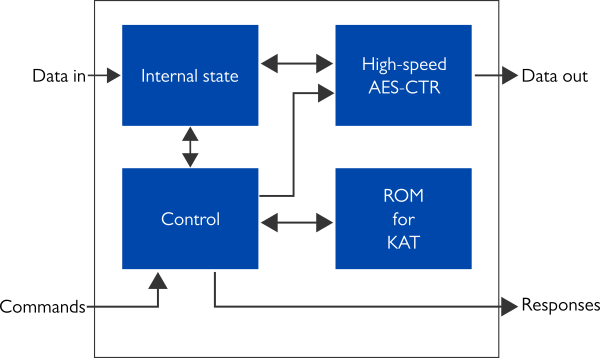

Both of the newly launched PRNG IP cores are based on the standardised use of CTR_DRBG defined in SP800-90A with 256-bit AES. The balanced version XIP8103B achieves a throughput in the gigabits per second (Gbps) range, and the high-speed version XIP8103H outputs random data at the rate of tens of gigabits per second speed. Importantly – and as required by the standards – both of the newly launched PRNG IP cores need to be periodically re-seeded with fresh randomness from a full entropy source, such as Xiphera’s TRNG IP core.

“Randomness – besides being critically important for cryptography – is also a mathematically fascinating topic”, says Perttu Saarela, Cryptographic Engineer at Xiphera, “Designing the PRNG IP cores was a great challenge, both as an engineer and as a mathematician.”

For more information, visit Xiphera’s PRNG product page and the Random Number Generation product family page.

Open the full product briefs for XIP8103B and XIP8103H.

If you’re interested to learn more about randomness, watch our webinar ‘What Everyone Should Know about Randomness?’.