Ascon

The lightweight Ascon IP core is ideal for constrained environments such as IoT devices.

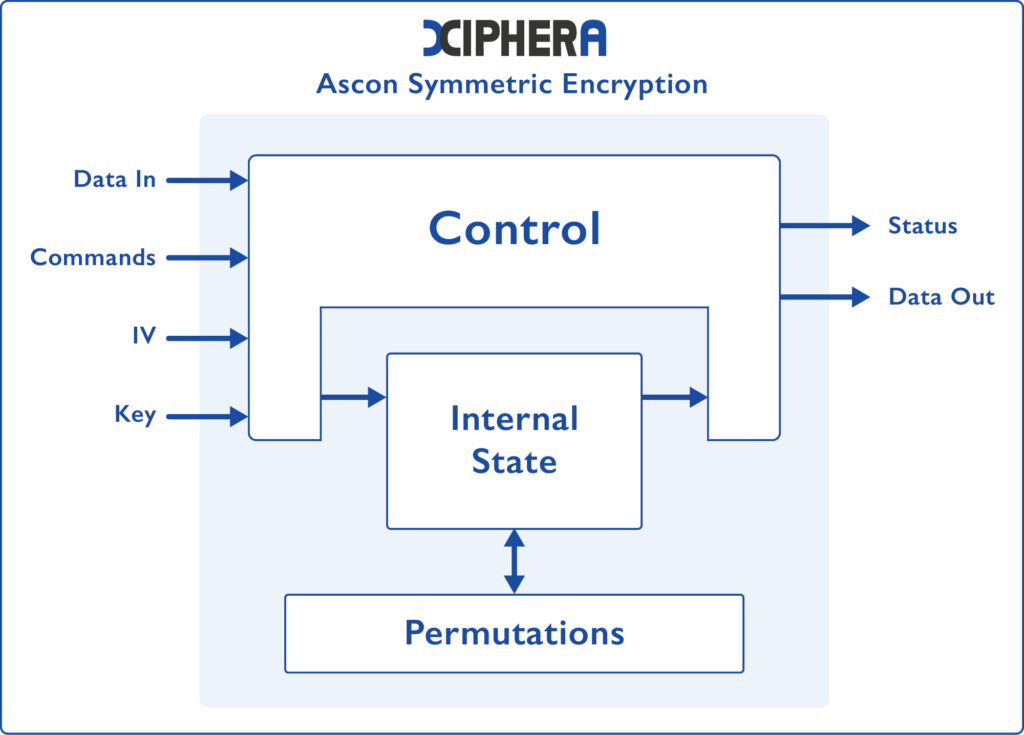

Ascon IP core implements a lightweight, sponge-based encryption algorithm, being ideal for constrained environments such as IoT devices. Ascon performs three cryptographic primitives: Authenticated Encryption with Associated Data (AEAD), hashing, and extendable output function (XOF), offering a smaller alternative for e.g. AES-GCM and SHA-3 IP cores. Xiphera’s in-house designed Ascon IP cores is optimised for efficiency and optimal performance in both FPGA and ASIC implementations.

Enhance your security with advanced encryption engines for…

IoT devices

Wearables

Low-power devices and constrained environments

Key features

- Optimised resource requirements

- Versatile algorithm support for AEAD, hashing, and XOF

- Compliant with modern cryptographic standards

- Quantum-secure with 256-bit key length

- Pure RTL without hidden CPU or software components

- Easy system integration

- Vendor agnostic FPGA/ASIC implementation

Technical specifications

The lightweight Ascon algorithm is ideal for constrained environments, such as IoT devices.

Balanced Ascon IP core

Product code: XIP2201B

- 100s of Mbps

- Only ~2.3 kLUTs

Product brief

Learn more about the key features and functionalities of the Ascon IP core.

Resource sheet

Download the resource sheet to learn more about the FPGA and ASIC resource requirements and performance.

AES-GCM for confidentiality and authenticity

AES-GCM is a widely used cryptographic algorithm for Authenticated Encryption with Associated Data (AEAD) purposes, providing both data confidentiality and authenticity. Xiphera offers AES-GCM cores for both optimal efficiency and high performance.