AES-GCM

Xiphera’s AES-GCM IP cores provide data confidentiality and authenticity. Our extreme-speed AES-GCM achieves hundreds of Gbps of throughput.

AES-GCM IP cores implement the Advanced Encryption Standard (AES) in Galois Counter Mode (GCM). AES-GCM is a widely used cryptographic algorithm for Authenticated Encryption with Associated Data (AEAD) purposes, providing both data confidentiality and authenticity. AES-GCM IP cores work as building blocks in various cryptographic IP cores in Xiphera’s portfolio. The in-house designed, CAVP-validated AES-GCM cores are available for both optimal efficiency and high performance in both FPGA and ASIC implementations.

Enhance your security with advanced AES-GCM encryptions for…

MACsec, IPsec, and TLS protocols

Secure data communication

Data centre and cloud environments

Key features

- Optimised resource requirements

- High throughput – up to hundreds of Gbps

- Compliant with NIST standards

- CAVP validated by NIST

- Support for all key lengths (128, 192, 256 bits)

- Pure RTL without hidden CPU or software components

- Easy system integration

- Vendor agnostic FPGA/ASIC implementation

Technical specifications

Xiphera’s AES IP cores offer various modes, ensuring performance, flexibility, and robust security.

Balanced AES256-GCM

Product code: XIP1113B

- Hundreds of Mbps

- ~3 kLUTs

- CAVP validated IP core

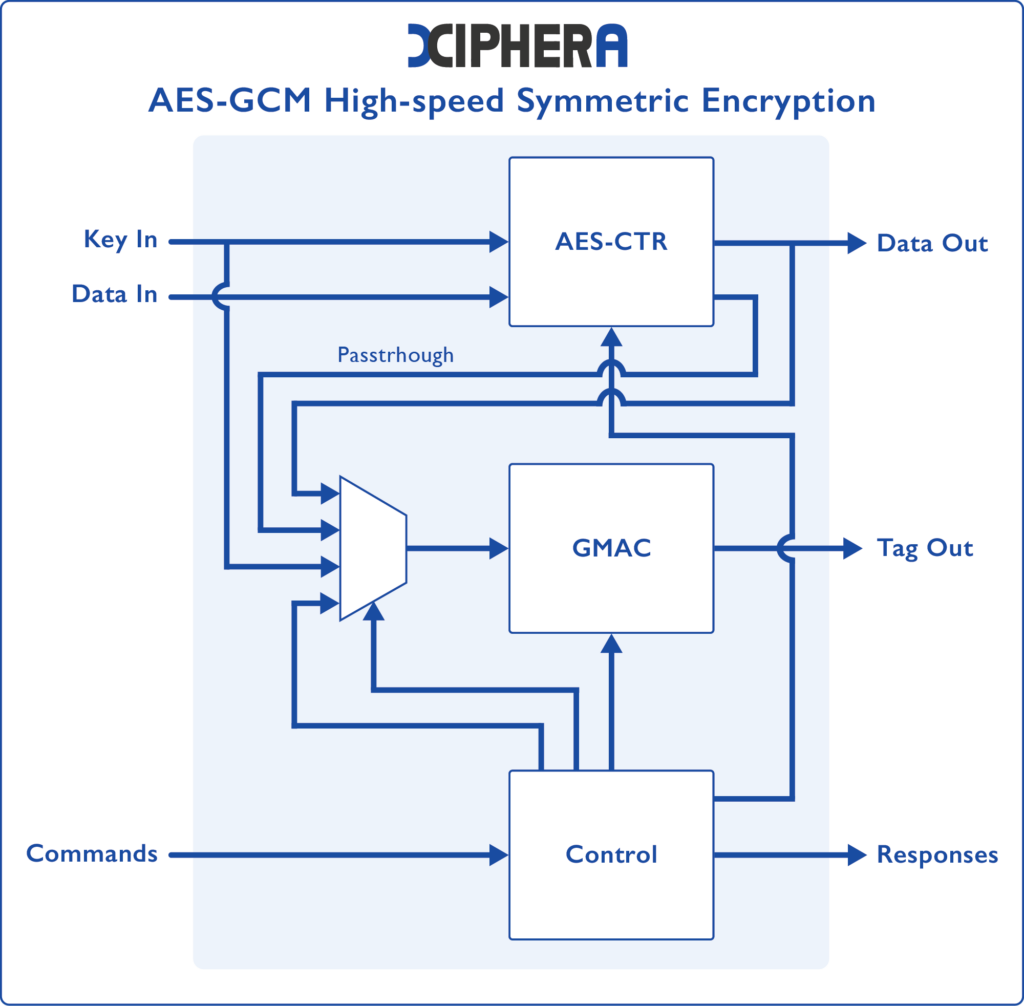

High-speed AES256-GCM

Product code: XIP1113H

- Up to 100 Gbps

- ~26 kLUTs

- CAVP validated IP core

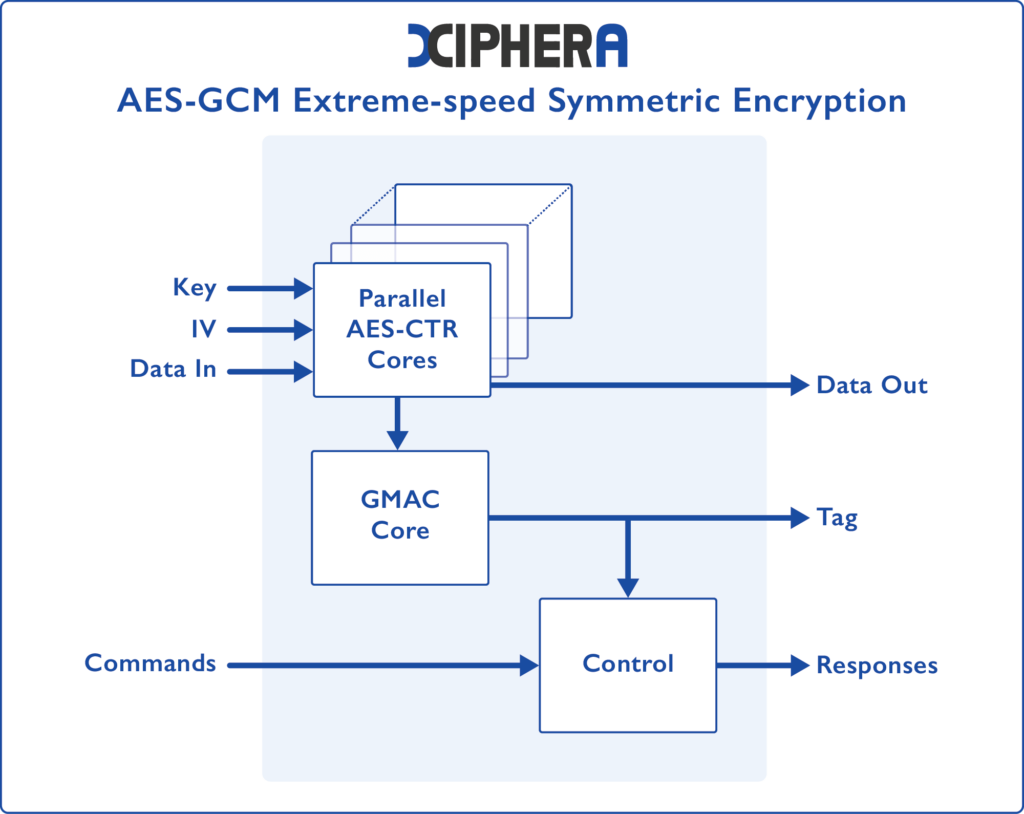

Extreme-speed AES256-GCM

Product code: XIP1113E

- Hundreds of Gbps

- Starting from 60 kLUTs

- CAVP validated IP core

Product brief

Learn more about the key features and functionalities of the AES-GCM IP cores.

Resource sheet

Download the resource sheet to learn more about the FPGA and ASIC resource requirements and performance.

Symmetric encryption for cryptographic protocols

The AES-GCM IP cores are essential building blocks in various cryptographic implementations, including solutions in Xiphera’s Security Protocol family. Xiphera offers a wide selection of security protocols for designers to protect the data in transfer through the most critical communication layers of the OSI model.