Versatile AES

Xiphera’s Versatile AES IP core ensures data confidentiality by supporting AES with a 256-bit key in five widely used selectable modes.

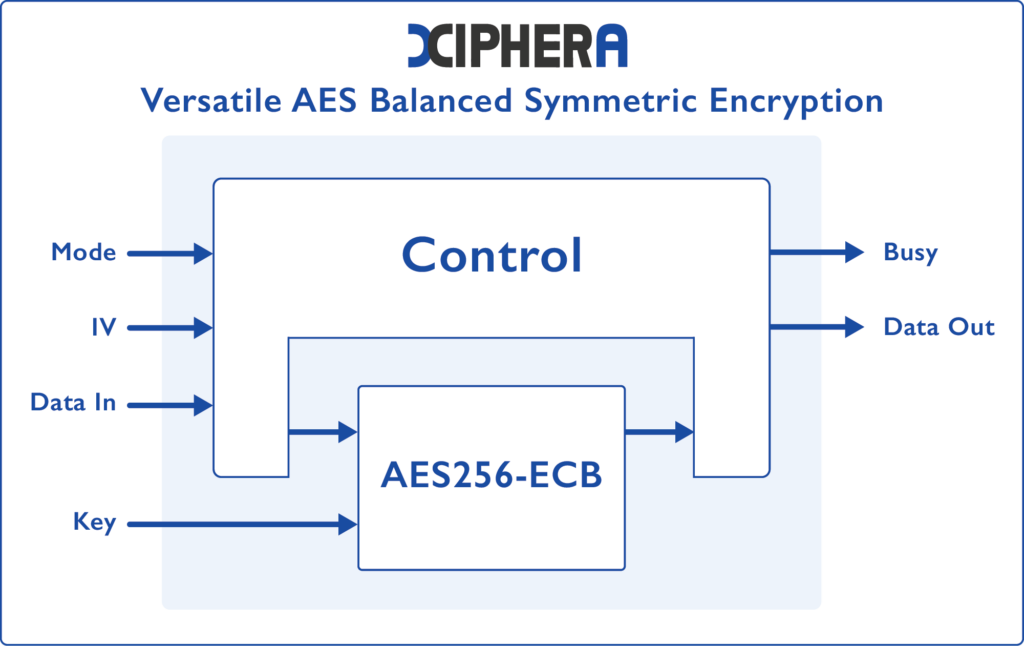

Xiphera’s Versatile AES IP core implements the Advanced Encryption Standard (AES) with a 256-bit key in five selectable modes: ECB, CBC, CFB, OFB, and CTR. All of these modes ensure data confidentiality and are widely used in security designs and cryptographic protocols. Xiphera’s in-house designed, CAVP-validated Versatile AES IP core has been designed for easy integration with FPGA- and ASIC-based designs in a vendor-agnostic design methodology.

Enhance your security with advanced AES-GCM encryptions for…

Industrial automation environments

Secure data communication

IoT security

Key features

- Optimised resource requirements

- CAVP validated by NIST

- Support for various AES modes including CTR, ECB, CBC, CFB, and OFB

- Compliant with NIST AES standard and the listed modes of operation

- Pure RTL without hidden CPU or software components

- Easy system integration

- Vendor agnostic FPGA/ASIC implementation

Technical specifications

Xiphera’s AES IP cores offer various modes, ensuring performance, flexibility, and robust security.

Balanced Versatile AES

Product code: XIP1123B

- Several Mbps

- Only ~4 kLUTs

- CAVP validated IP core

Supported modes of operation

- Electronic Codebook (ECB)

- Cipher Block Chaining (CBC)

- Cipher Feedback (CFB)

- Output Feedback (OFB)

- Counter (CTR)

Product brief

Learn more about the key features and functionalities of the Versatile AES IP core.

Resource sheet

Download the resource sheet to learn more about the FPGA and ASIC resource requirements and performance.

AES-GCM for confidentiality and authenticity

AES-GCM is a widely used cryptographic algorithm for Authenticated Encryption with Associated Data (AEAD) purposes, providing both data confidentiality and authenticity. Xiphera offers AES-GCM cores for both optimal efficiency and high performance.