True Random Number Generation (TRNG)

The TRNG IP core generates high-entropy, true random numbers essential for secure communications and cryptographic operations, such as key generation.

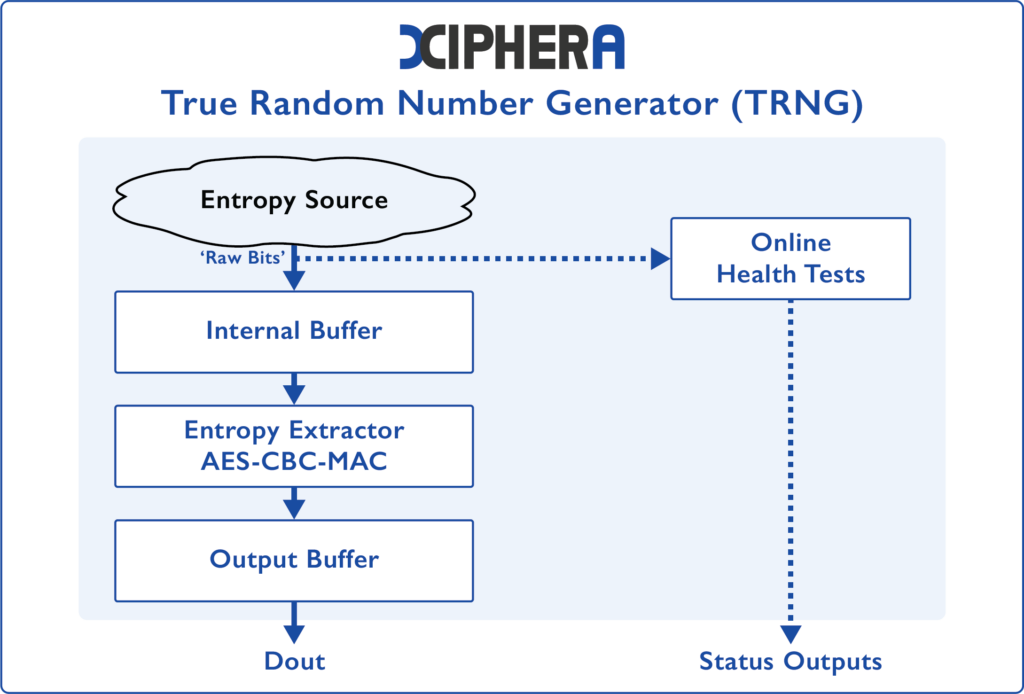

The True Random Number Generator (TRNG) IP core establishes a benchmark for hardware-based security in cryptographic systems, by generating high-entropy, true random numbers essential for secure communications and cryptographic operations, such as key generation. It includes a robust and thoroughly characterised entropy source, online health tests and a proven AES-CBC-MAC-based entropy extractor.

The TRNG IP core conforms to the stringent requirements of NIST standards and widely used test suites, while offering flexibility and broad compatibility for both FPGA and ASIC designs. It is an essential component of security protocols such as TLS 1.3 and MACsec.

Enhance your security with high-entropy TRNG for...

Space and satellite applications

Defense and mission-critical communications

VPN, TLS, IPsec, and MACsec

Automotive systems and wearables

Key features

Moderate resource requirements

Compliant with NIST SP 800-22 / SP 800-90B

Ready for FIPS 140-3 certification

AES-CBC-MAC-based entropy

Security features (e.g. zeroise function)

Passes PractRand, gjrand, TestU01, and dieharder test suites

Parameterisable design

Easy system integration

Vendor agnostic FPGA/ASIC implementation

Technical specifications

The TRNG core integrates robust health monitoring systems to ensure the highest level of randomness and security under any operational conditions.

Combining the TRNG with our NIST SP800-90A compliant PRNG provides a NIST SP800-90C compliant Random Number Generator, optimal for cryptographic security.

Balanced TRNG IP core

Product code: XIP8001B

Moderate resource requirements with no multipliers or DSP blocks

Tunable entropy source

Additional security features

Easily portable fully digital design

Product brief

Learn more about the key features and functionalities of the True Random Number Generator (TRNG).

Resource sheet

Download the resource sheet to learn more about the FPAG and ASIC resource requirements and performance.

High-quality pseudorandomness

Xiphera’s Pseudorandom Number Generation (PRNG) IP core provides randomness in applications, where lots of random data is needed, for example in the generation of session-specific secret key material in core network routers.