Pseudorandom Number Generation (PRNG)

The PRNG IP core establishes a benchmark for hardware-based security in cryptographic systems by generating high-quality pseudorandom numbers.

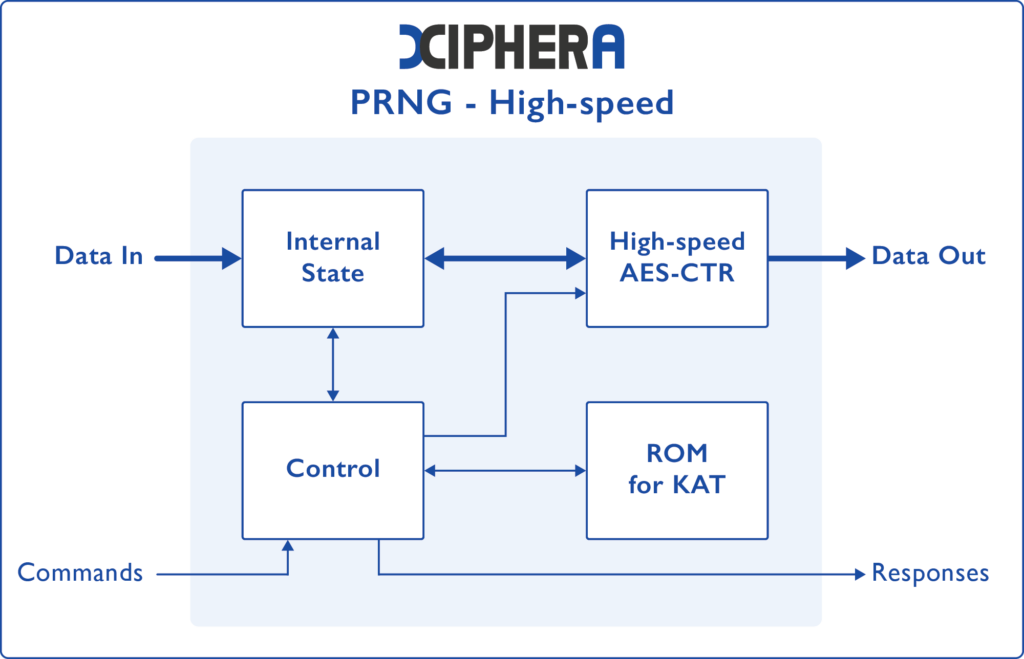

Xiphera’s Pseudorandom Number Generator (PRNG) IP core establishes a benchmark for hardware-based security in cryptographic systems by generating high-quality pseudorandom numbers. It delivers accelerated output rates essential for secure communications and cryptographic operations, such as key generation. It includes robust and thoroughly characterised initialisation and reseeding mechanisms and a proven CTR_DRBG and AES-256 based pseudorandom number generator.

The PRNG IP core conforms to the stringent NIST requirements while offering flexibility and broad compatibility for both FPGA and ASIC designs.

High-quality, high-output PRNG for security & performance in...

Space and satellite applications

Defense and mission-critical applications

Quantum Random Number Generator

Industrial automation and Automotive solutions

Key features

Moderate resource requirements

- High output rate – up to tens of Gbps

Compliant with NIST SP 800-90A

- CAVP validated

Ready for FIPS 140-3 certification

CTR_DRBG with AES-256

Support backtracking resistance

Forward prediction resistance mode

Parameterisable and fully digital design

Easy system integration via AXI4 interface

Vendor agnostic FPGA/ASIC implementation

Technical specifications

Combining the PRNG with our NIST SP800-90B compliant TRNG, provides a NIST SP800-90C compliant Random Number Generator, optimal for cryptographic security.

Balanced PRNG IP core

Product code: XIP8103B

Over 2 Gbps output

Only ~4 .1 kLUTs in a typical FPGA setup

- CAVP validated IP core

High-speed PRNG IP core

Product code: XIP8103H

Suitable for high-throughput environments

Over 69 Gbps output

Only ~18 kLUTs in a typical FPGA setup

- CAVP validated IP core

Product brief

Learn more about the key features and functionalities of the PRNG IP cores.

Resource sheet

Download the resource sheet to learn more about the FPGA and ASIC resource requirements and performance.

High-entropy, true randomness with TRNG

Xiphera’s PRNG IP cores are periodically re-seeded with fresh randomness from a full entropy source, such as Xiphera’s True Random Number Generator (TRNG) IP core. The TRNG IP core generates high-entropy, true random numbers for secure communications and cryptographic operations.