Xiphera introduces Extreme-Speed Solutions in its cryptographic IP core portfolio, by launching two new extreme-speed IP cores, for AES-GCM and MACsec. The AES-GCM and MACsec products are the first extreme-speed (E) product variants in Xiphera’s portfolio that already comprises C for compact, B for balanced, and H for high-speed IP core variants.

Xiphera focuses on speed also for asymmetric encryption algorithms, by introducing a new high-speed IP core for Elliptic Curve Cryptography (ECC). This new high-speed variant offers significantly enhanced speed performance, adding a completely new product option in Xiphera’s already extensive Asymmetric Cryptography portfolio.

Introducing the Extreme-Speed Solutions

Xiphera’s Extreme-Speed Solutions offer new extreme-speed (E) variants of Xiphera’s IP cores, targeted for applications with highest performance requirements, such as encryption of backbone networks or peripheral component interfaces.

Xiphera’s high-speed (H) IP core variants already provide encryption throughput of tens of gigabits per second (Gbps). The extreme-speed variants push performance beyond hundreds of Gbps for a single stream of data, and are more than just simple parallelisations of the H variant.

Three new IP cores for enhanced performance

Xiphera’s new Extreme-Speed Solutions offer the E variants for the AES-GCM and MACsec IP cores.

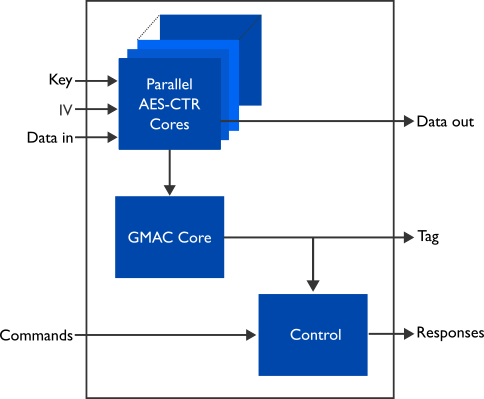

AES-GCM protects confidentiality and authenticity of communication, for example, in MACsec, IPsec, and TLS protocols. The new extreme-speed AES-GCM IP core utilise wider data widths (e.g. 256 and 512 bits), reaching throughputs of several hundreds of Gbps in modern FPGA and ASIC technologies. Xiphera’s AES-GCM cores have a constant latency for use with timing sensitive protocols and offering full protection against timing-based attacks.

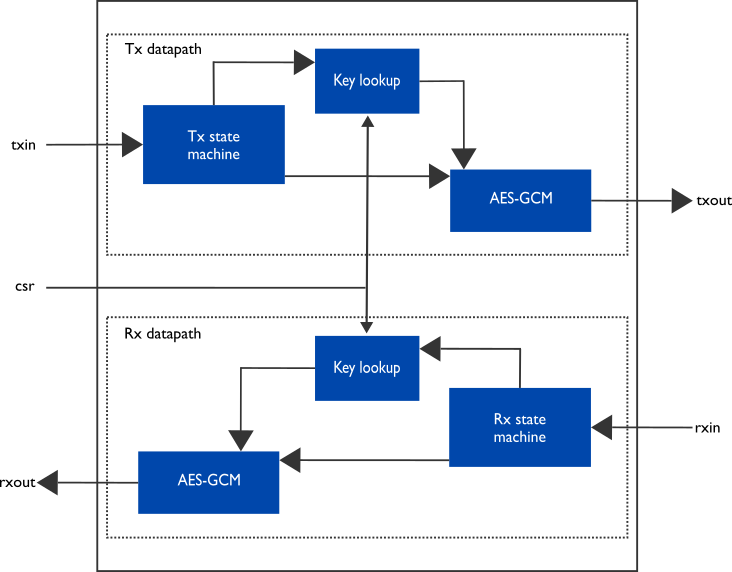

Extreme-speed MACsec IP core protects 100 Gbps MACsec communication. It utilises the new AES-GCM E variants and is compliant with the MACsec protocol using 256-bit AES-GCM. Xiphera will extend the offering with further speed grades in the future. The 100G MACsec is compatible with timing sensitive protocols and is fully protected against timing attacks.

“We are very excited by the introduction of the first products in our Extreme-Speed Solution offering”, says Kimmo Järvinen, Xiphera’s co-founder and CTO. “Xiphera is now even better positioned to solve the most demanding encryption requirements for our customers.”

Xiphera also announces the high-speed ECC IP core, pushing the speed of Xiphera’s asymmetric cryptography offering to a completely new level. The new high-speed variant supports Elliptic Curve Diffie-Hellman (ECDH) and Elliptic Curve Digital Signature Algorithm (ECDSA), reaching to more than a thousand operations per second in a modern FPGA or ASIC. It covers all NIST P curves with a single IP core instance and also allows the use of user-specified elliptic curves. The IP core also offers an option for hardened protections against multiple trace side-channel attacks.

Find more about Xiphera’s Extreme-Speed Solutions.

Visit the product page for AES-GCM. You can also open the product brief as PDF.

Visit the product page for MACsec. You can also open the product brief as PDF.

Visit the product family page for Asymmetric Cryptography. For more information about the high-speed ECC IP core, contact us.