When you think of cryptographic applications, the first thing that usually comes to your mind is protecting data in motion, such as protecting Internet traffic with Transport Layer Security (TLS) or securing Ethernet traffic with MACsec. However, securing and protecting data at rest – meaning inactive data stored on any mass storage media – is equally important, especially when you consider the staggeringly large amount of data generated each day by the humankind.

To address the needs to secure data at rest, Xiphera has expanded its product portfolio by adding two Intellectual Property (IP) cores, XIP1183B and XIP1183H, to its offering. The freshly added IP cores are based on the AES-XTS, which is the most popular standard for encrypting data on block-oriented storage devices and formally defined in IEEE Standard 1619-2018.

“Sensitive data at rest may well need to be secured for decades, and therefore Xiphera has focused on 256-bit security level in our AES-XTS portfolio to make them resistant even against the projected advances in quantum computing”, says Kimmo Järvinen, Co-founder and CTO of Xiphera.

Technical details

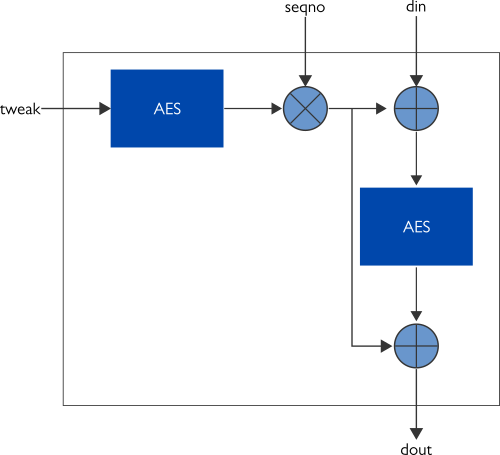

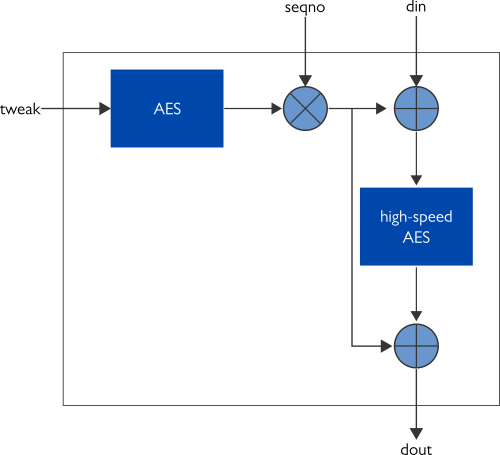

Technically, XTS is a mode of operation, which instantiates the underlying AES block cipher twice. The encrypted data depends not only on the plaintext and encryption key, but also on the logical address of the data on the storage device, which means that identical plaintexts get encrypted differently at different logical addresses.

As an example of the technical features of Xiphera’s AES-XTS IP cores, the performance-optimised version XIP1183H achieves an encryption/decryption throughput of more than 50 Gbps in high-end FPGAs, and even higher throughput rates are possible by instantiating the IP core in parallel.

Below are the illustrations of the internal high-level block diagrams of XIP1183B and XIP1183H.

For more information, visit the product pages for the balanced version XIP1183B and the high-speed version XIP1183H. You can also view and download the full product briefs for XIP1183B and XIP1183H.

Read more about Advanced Encryption Standard and see more of the solutions of this product family from our Block/stream ciphers pages. Don’t hesitate to contact us at sales(at)xiphera.com.