Speed is nothing without security

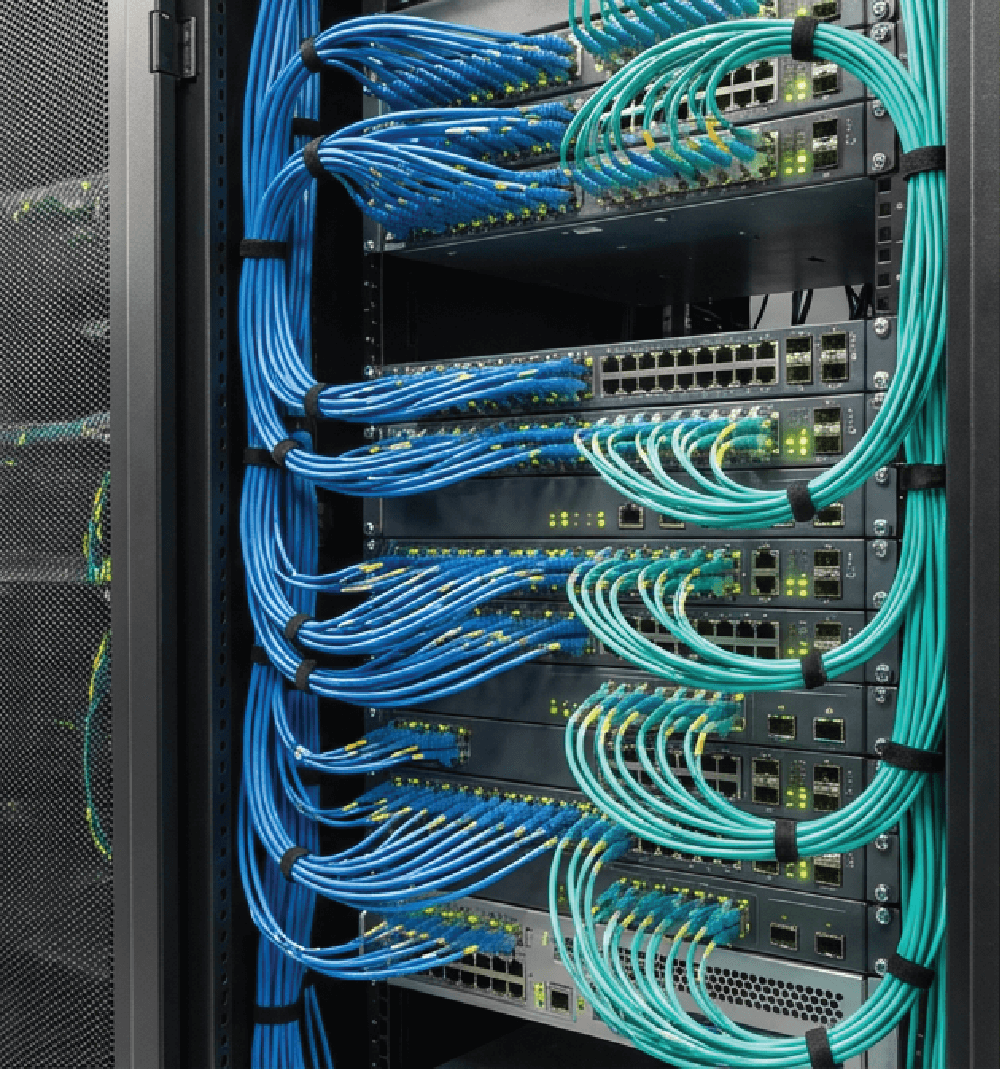

Hardware-based cryptography for high-performance telecommunications and data centres

Friction is the enemy of high-speed data

Independent cryptography vendor, securing global telecom and data centre infrastructures

Telecommunications and data centres cannot afford bottlenecks. Xiphera’s hardware-based cryptographic IP cores secure critical network traffic, while maintaining full line-rate performance in high-speed environments.

Remove challenges with

Xiphera high-speed IP

100G and beyond

throughput

Hardware-based cryptography that delivers true line-rate security.

Predictable

latency

Encryption that maintains full network performance in demanding telecom and data centre environments.

Protocol security

across the OSI model

Support for MACsec, IPsec, TLS 1.3, and other standardised communications protocols.

One code base

for FPGA and ASIC

Highly portable IP cores designed for an efficient transition to ASIC, when product volumes grow.

Xiphera's hardware security highlights for Telecom and Data Centers

MACsec

Protects high-speed link-layer connections by securing traffic directly between network ports, while maintaining full switching performance. The underlying crypto engines in the MACsec solutions are based on Xiphera’s own AES-GCM IP (Intellectual Property) cores.

IPsec

Secures IP traffic with authenticated and encrypted tunnels between network domains, to protect data in motion across critical network interconnects. IPsec implementation can be adapted based on customer requirements and the selected hardware architecture.

TLS 1.3

Enables secure application- level communication, with fully hardware-based key handling to minimize latency and reduce exposure to software threats. Xiphera TLS 1.3 IP cores maintain a compact footprint, making them exceptionally well-suited for high-volume applications.

AES-GCM

The AES-GCM IP cores provide data confidentiality and authenticity for satellite to ground station communications. In-house designed and CAVP-validated, they deliver extreme-speed performance of hundreds of Gbps and are optimized for both FPGA and ASIC implementations.

Standards-based and validated solutions

- NIST-compliant hardware cryptography for critical network infrastructure

- CAVP-validated cryptographic IP cores for silicon-level security

- Designed for high-performance telecom and data centre systems

- Expert support throughout the entire integration lifecycle

Securing critical infrastructure with cryptography

We explain how hardware-based cryptography protects high-speed telecommunications and data centre networks. Security must keep up with line-rate performance to avoid bottlenecks. Xiphera ensures critical connectivity stays secure and uninterrupted.

FAQ

Can Xiphera meet high network speed requirements?

Yes. Xiphera’s hardware-based cryptographic IP cores deliver true line-rate performance, even at speeds of hundreds of Gbps, without creating bottlenecks.

Why is hardware security important for telecom networks and data centres?

Hardware-based encryption ensures low and predictable latency, keeping critical switching, routing and SmartNIC workloads fully protected without slowing the network.

Can Xiphera support FPGA and ASIC projects?

Yes. Our IP cores use one code base for efficient migration from FPGA prototypes to high-volume ASIC deployments

Are Xiphera’s solutions standards-aligned?

Yes. We implement widely adopted protocol standards such as MACsec, IPsec, and TLS 1.3, as well as NIST-approved algorithms such as AES-GCM.