AES-CTR

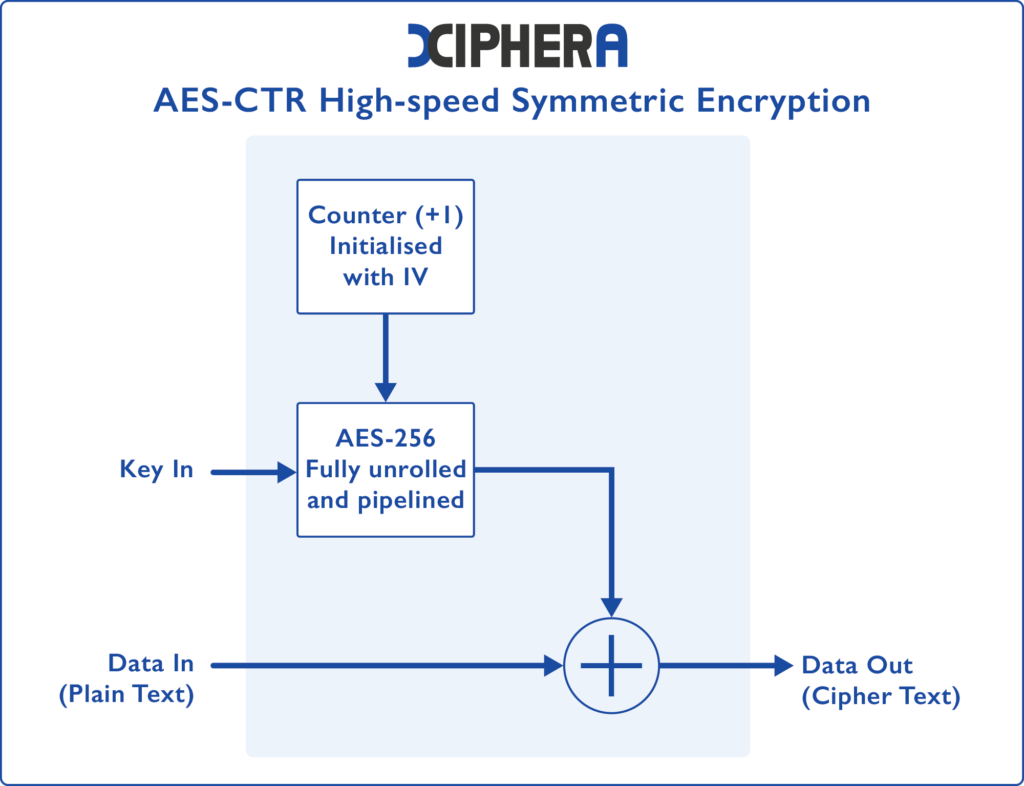

Xiphera’s AES-CTR IP cores implement the AES in Counter mode, effectively turning a block cipher into a stream cipher while providing multiple implementation advantages.

AES-CTR IP core implements the Advanced Encryption Standard (AES) in Counter Mode (CTR). The IP core effectively turns a block cipher into a stream cipher, and provides a number of advantages for optimising resource usage and performance. Xiphera’s in-house designed, CAVP-validated, and vendor-agnostic AES-CTR core has been designed for easy integration with FPGA and ASIC-based designs.

Enhance your security with AES-CTR encryptions for…

Secure communications

Industrial automation environments

IoT security

Key features

- CAVP validated by NIST

- Compliant with NIST standards

- High throughput – up to hundred Gbps

- Pure RTL without hidden CPU or software components

- Easy system integration

- Vendor agnostic FPGA/ASIC implementation

Technical specifications

Xiphera’s AES IP cores offer various modes, ensuring performance, flexibility, and robust security.

High-speed AES256-CTR

Product code: XIP1103H

- Up to 100 Gbps

- ~15 kLUTs

- CAVP validated IP core

Product brief

Learn more about the key features and functionalities of the AES-CTR IP core.

AES-GCM for confidentiality and authenticity

AES-GCM is a widely used cryptographic algorithm for Authenticated Encryption with Associated Data (AEAD) purposes, providing both data confidentiality and authenticity. Xiphera offers AES-GCM cores for both optimal efficiency and high performance.