IPsec

Xiphera’s IPsec cores ensure the authenticity and confidentiality of data traffic. The scalable, extreme-speed IPsec IP cores are tailored for high-bandwidth applications.

IPsec (Internet Protocol Security) is a widely implemented protocol to secure communications across the Internet. Xiphera’s IPsec IP core enhances secure communication at layer three (Network) of the OSI model, ensuring the authenticity and confidentiality of data traffic. It leverages the Advanced Encryption Standard (AES) in Galois Counter Mode (GCM) with a 256-bit key length, to secure device communications with the IPsec protocol.

Xiphera’s scalable extreme-speed IPsec IP cores are tailored for high-bandwidth applications, ranging from 10 Gbps to 200 Gbps links. Designed for seamless integration, our IP cores support a vendor-agnostic design methodology, making them adaptable across various high-end FPGA or ASIC environments.

Enhance your network with advanced IPsec protections for...

Data Center, cloud, and edge security

Virtual Private Networks (VPNs)

FPGA-based SmartNICs

Key features

Moderate resource requirements

High throughput up to 100s of Gbps

Powered by AES256-GCM

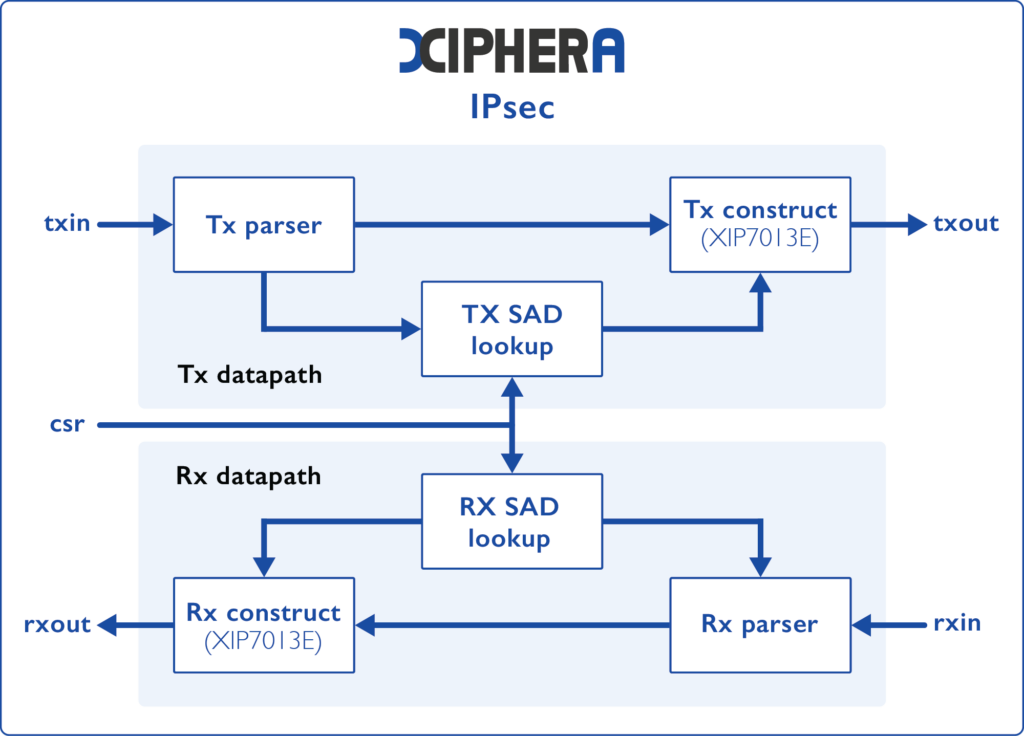

Support for encryption and decryption

Streaming interface for simple integration

Independent Receive and Transmit channels

Efficient and optimised architecture

Easy system integration

Vendor agnostic FPGA implementation

Technical specifications

IPsec implementation can be adapted based on customer requirements and the selected hardware architecture.

Flexible packet processing enables authentication and encryption with or without Initialisation Vector, or passing payload as it is.

Optimisable implementation adapts to customer requirements and hardware architecture.

Standalone IPsec

Product code: XIP7213E

- Standalone IPsec protocol implementation

- Compliant with RFC 4303 and RFC 4035

- Tunnel and Transport mode support

- Up to 256 Security Associations

- Flexible key management interface

ESP Frame AEAD

Product code: XIP7013E

- Moderate resource requirements with no multipliers or DSP blocks

Encapsulating Security Payload (ESP) frame AEAD processing

Compliant with RFC 4303

Product brief

Learn more about the key features and functionalities of the IPsec IP cores.

Resource sheet

Download the resource sheet to learn more about the FPGA and ASIC resource requirements and performance.

Protection with extreme-speed performance

The underlying crypto engines in the MACsec solutions are based on Xiphera’s own AES-GCM IP (Intellectual Property) cores. With the introduction of our extreme-speed AES-GCM core, we offer extreme-speed IPsec and extreme-speed 100G MACsec IP cores.