Hardware-based security solutions with strong cryptographic expertise

Peace of mind in a dangerous world

Customers across 4 continents trust Xiphera

Reasons to choose Xiphera

When security is not negotiable, Xiphera protects your critical systems with quantum-resistant and traditional cryptography, implemented in pure hardware logic for the highest level of protection.

Comprehensive

Portfolio

A complete set of FPGA- and ASIC- based cryptographic IP cores for secure communication, data protection, and authentication.

Deep Cryptographic

Expertise

All design and development takes place in Finland, ensuring full supply chain visibility and trustworthy technology.

True Hardware-based

Cryptography

No CPU and no software. Pure hardware logic reduces attack risks, provides consistent performance, and supports low-power designs.

Post-Quantum

Ready

Our PQC-enabled IP cores protect sensitive data for decades, ensuring security today and resilience against future threats.

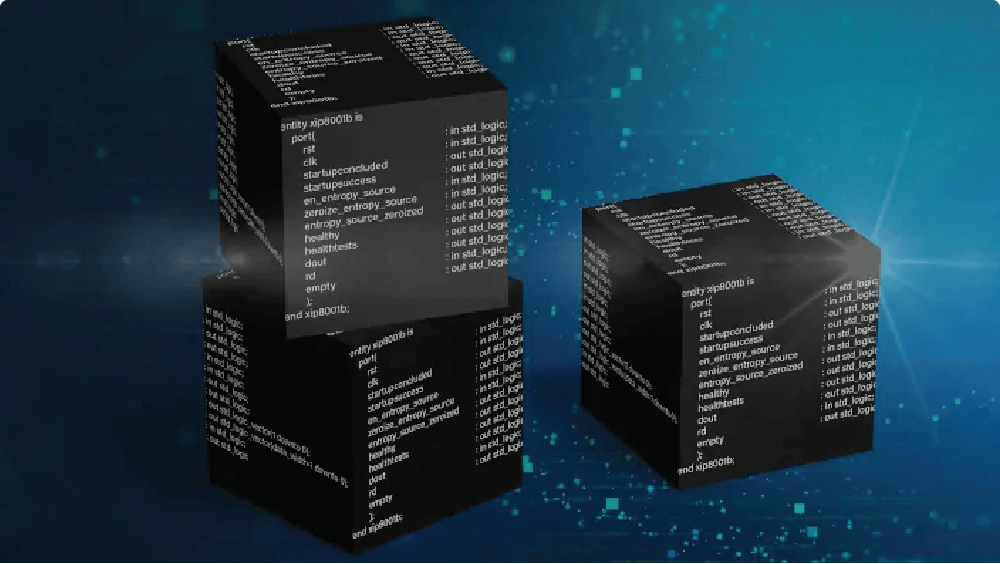

Highlights of Xiphera’s ASIC & FPGA crypto solutions

We deliver hardware-based cryptography that ensures your systems and data remain secure, reliable, and future-proof.

nQrux®

Secure Boot

Ensures processor startup security by verifying the authenticity and integrity of binary images. Uses a hybrid quantum-resistant signature scheme (ML-DSA) with ECDSA fallback to protect against both classical and quantum threats.

True Random

Number Generation

Xiphera’s TRNG IP core generates high-entropy, true random numbers for secure communications and cryptographic operations. Compatible with FPGA and ASIC, it meets NIST standards and supports protocols like TLS 1.3 and MACsec.

xQlave® Post-Quantum

Cryptography

The xQlave® family provides quantum-secure cryptographic IP cores, including ML-KEM (kyber) key encapsulation mechanism and ML-DSA (dilithium) digital signature IP cores. These solutions protect sensitive information against the imminent quantum threat.

Security

Protocols

Xiphera’s cryptographic Security Protocol portfolio, including widely used MACsec, IPsec, and TLS 1.1 protocols, secures point-to-point communication as well as server-client connections over the Internet.

nQrux®

Crypto Module

Xiphera’s nQrux® Crypto Module IP core provides a comprehensive security platform that allows for customisation of top-notch cryptographic services, suitable for both microcontrollers and SoC systems.

In Co-Operation With

Xiphera - Securing Industries Worldwide

Across industries with the highest security requirements, Xiphera provides hardware-based cryptography that combines reliability, performance, and long-term protection.

Why Hardware-based Cryptographic IP Cores?

- Easy certification and validation

- FPGA and ASIC support for long device lifecycles

- Low power consumption

- Pure digital logic – no software, no hidden firmware

- Predictable performance and latency

- Minimal attack surface